劉細鳳

安科瑞電氣股份有限公司 上海嘉定 201801

摘要:本文基于霍爾傳感器輸出信號幅度小、頻率低、易受噪聲干擾的特點,有針對性地提出種基于高頻調制方式實現的霍爾傳感器讀出電路。該讀出電路主要包括可變增益運算放大器,高頻調制電路以及1bit量化的二階sigma-delta模數轉換器。通過采用高頻調制,減少電路中低頻噪聲以及失調的影響,同時經過放大器進行幅值放大,避免噪聲混入。先通過MATLAB建模仿真確定設計所需參數,然后基于SMIC0.18Ixm混合信號CMOS工藝完成整體電路設計。經測試,電路在3.3V電源電壓,1kHz信號帶寬以及256kHz時鐘頻率下,經過后仿真得到信噪比(SNR)為83.12dB,可滿足設計的要求。

關鍵詞:爾傳感器讀出電路;高頻調制電路;可變增益放大器;調制器

0引言

隨著霍爾傳感器廣泛應用于電子、、器械等各個方面,對其輸出信號進行準確采集變得至關重要。經研究發現,在3.3V電源電壓,±0.4T磁場強度條件下,霍爾傳感器輸出信號范圍在±150mV之間。而在通常應用中,霍爾傳感器大多處在較小的磁場里,般為mT數量級,因此霍爾傳感器的輸出信號較小,容易受到外界環境的干擾,需要對輸出信號進行放大處理。同時,基于輸出信號頻率較低的特性,需要采用低頻噪聲抑制電路來降低噪聲對信號帶來的影響。zui后以模數轉換器作為信號進行數據轉換與精度測量的模塊也是*的。

外對于讀出電路的研究已經較為成熟,而內近些年來也有較大發展,如上海華虹、中科學院微電子所以及中科學院大學在讀出電路設計方面都有相應成果,本文在這些研究基礎上加入噪聲抑制電路,進步改善讀出電路的性能。

霍爾傳感器讀出電路的設計如圖1所示,主要由對信號進行放大的可變增益放大器以及對信號進行轉換的模數轉換器組成。其中,為避免低頻噪聲和失調的影響,在設計中加入了高頻調制結構,將噪聲和失調轉移到信號帶寬之外,以改善整體電路性能。

圖1霍爾傳感器讀出電路結構

本文詳細介紹了讀出電路芯片的設計,對電路的基本理論與架構進行研究與分析,完成從Simulink建模,電路設計到版圖布局各個環節,zui終進行后仿真,實現目標要求。

1整體電路建模

從讀出電路基本理論與架構出發,基于MATLAB平臺對于整體電路結構進行模型仿真。如圖2所示,框圖由上到下分別為基于高頻調制的可變增益運算放大器,sigma—delta調制器以及降采樣數字濾波器。具體流程如下:可變增益運算放大器根據輸入信號幅度大小自動選擇合適的放大倍數進行信號放大。放大后的信號由sig-ma-delta調制器進行積分量化,轉化為1bit的數字信號,然后經過后級降采樣數字濾波器的濾波和抽樣過程,輸出高精度的數字碼。

幽2讀出電路的MATLAB模型

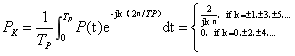

該設計提出在運算放大器的輸入與輸出節點加入高頻調制電路,其目的主要是將運放產生的1/f噪聲和失調調制到信號帶寬之外,然后在濾波器的作用下濾除掉,避免噪聲和失調對低頻小信號產生影響。因此高頻調制電路的功能主要是完成對噪聲信號的調制。由傅里葉級數可知:假設P是周期為TP占空比為50%的方波信號。傅里葉系數設為PK。由此可以得到:

(1)

(1)

若將噪聲的功率譜密度(PSD)設為Sn(w),則經過次調制的噪聲功率譜密度Sn(w)可以表示為:

(2)

(2)

由式(2)可以得出:噪聲頻譜Sn經過次調制被轉移到斬波信號P的奇次諧波上,因而削弱了信號基帶內的噪聲。而在高頻調制電路模型搭建過程中,高頻調制電路的頻率應滿足:

(3)

(3)

其中,K≥2,BWsignal為信號帶寬,fcorner,為噪聲角頻率。

而對于調制器的設計,則應先確定其噪聲傳輸函數。因為調制器的功能相當于低通的模擬濾波器,所以可以根據巴特沃茲濾波器的特性來對其進行分析,得到二階單環調制器的噪聲傳輸函數(NTF)為:

(4)

(4)

基于式(4),由調制器的架構,可以推導所需增益以及反饋因子的范圍,然后帶入模型進行仿真,確定合適的值。

由于sigma-delta模數轉換器的整體電路是由模擬調制器和數字濾波器共同構成,調制器部分決定設計的精度,而數字濾波器部分決定設計的面積和功耗,所以在對濾波器進行設計時,可以使用CIC濾波器、補償濾波器以及半帶濾波器的組合來盡可能的降低所需的硬件開銷,以減小電路的面積和功耗。

考慮實際電路設計中各種非理想因素如:KT/C噪聲、時鐘抖動、運放的有限增益、帶寬壓擺率以及開關非線性等的影響,確定模型中各個參數的指標。zui終得到仿真結果如圖3所示,信噪比達到84.2dB,達到預期74dB的設計目標。

圖3MATLAB模型仿真結果

2關鍵單元電路設計

2.1高頻調制電路

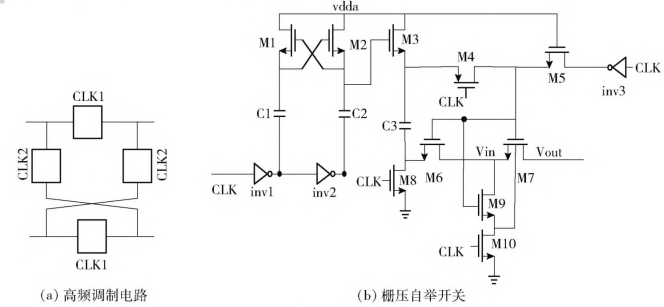

高頻調制電路作為降低電路噪聲及失調的關鍵模塊,其內部開關的結構如圖4(a)和圖4(b)所示。

圖4關鍵電路

由圖4(a)可知,在高頻調制電路中,隨著時鐘信號的交替變化,能夠選通不同的信號路徑,實現信號與方波相乘的功能。其中,對于方框中電路的選取只需要考慮信號能夠無損失傳輸即可。很簡單的情況是使用單個NMOS管來實現開關的功能,但是由于單個NMOS管做開關存在非線性以及閾值電壓變化的問題,會在電路中引入諧波失真,影響電路性能。所以本設計采用柵壓自舉開關的結構,如圖4(b)所示,當CLK為高電平時,M7管截止,M3和M8管導通,使得c3兩端的電壓為電源電壓;當CLK為低電平時,M3和M8管關斷,M4和M6導通,此時,M7也處于導通狀態且柵源電壓為C3兩端的電壓,因此與輸入信號的大小無關。即增加了開關導通電阻的線性度。同時柵壓自舉開關的使用方面避免了單個開關導通時電阻較大的問題,另方面也降低了時鐘饋通等因素的影響。

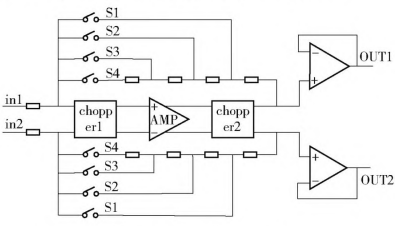

2.2可變增益運算放大器

由上述sigma-delta模數轉換器的模型結構可以驗證,在滿擺幅范圍內,隨著輸入信號幅度增加,模數轉換器的峰值信噪比(PSNR)也會增加,但是接近滿擺幅時,會引起調制器中后級積分器出現過擺幅的現象,從而在輸出引入大量諧波,使得PSNR下降。所以盡量選擇合適的信號幅值輸入。而霍爾傳感器處在不同磁場中,輸出信號幅度不同,這就使得通過轉換器轉換得到的精度產生很大差異。所以該設計在霍爾傳感器和模數轉換器之間加入可變增益的運算放大器,方面可以放大前端電路輸出的小信號,另方面又可以調節自身輸出信號幅度以適應后級模數轉換電路的要求,結構如圖5所示。

圖5可變增益運算放大器

在設計中,為保證電路穩定性,運放采用閉環結構。根據不同輸入信號的幅度大小,由數字電路控制選取不同的開關閉合,然后通過電阻比值對信號進行相應倍數的放大。其中對于阻值的選取,要考慮版圖的布局,以減小電阻失配誤差帶來的影響。此外,設計中加入了高頻調制電路,使得運放產生的1If噪聲和失調移到高頻端,以降低信號帶內噪聲。如圖6所示,虛線和實線分別為不加調制電路與加入調制電路的運放等效輸入噪聲的仿真結果,由圖6可以看出,高頻調制電路有效地抑制了低頻噪聲。

圖6不加與加入凋制電路的運放等效輸入噪聲波形

2.3sigma-delta調制器

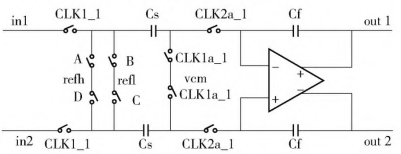

傳統的Nyquist模數轉換器利用復雜的比較方式實現對信號幅度精確量化的功能。但是由于近些年來工藝技術不斷發展,器件尺寸以及電源電壓不斷減小,器件的失配對于傳統模數轉換器的影響越來越大。而sigma-delta調制器利用其自身的環路調節勢,很大地減小了器件失配對電路精度的影響,易于實現高精度的轉換。調制過程的實質就是將信號帶內大部分噪聲移到帶外,再經過后級濾波器濾除,以提高信噪比,即提高轉換精度。該設計中sigma—delta調制器主要是由開關電容積分器、量化器、反饋DAC以及兩相非交疊時鐘4個模塊構成。

其中,積分器作為調制器實現低通濾波功能的主要模塊,結構如圖7所示,由兩相非交疊時鐘來控制電路的采樣與積分過程,同時為避免溝道電荷注入引入非線性誤差,在每個過程中,

控制靠近運放輸入端的開關先斷開,這樣避免了與輸入信號有關的電荷對運放輸出產生影響,但是這種方式會在電路中引入直流偏移,而直流偏移的影響能夠通過全差分結構來。

圖7積分器電路結構

在實際設計過程中,如果考慮運放有限增益以及寄生電容的影響,其傳輸函數為:

(5)

(5)

其中,![]() ,

,![]() 分別為積分器的增益誤差以及極點誤差。

分別為積分器的增益誤差以及極點誤差。

由式(5)可以看出,由于非理想因素的影響使得傳輸函數的極點由原點處發生了偏移,這樣會削弱積分器電路對于帶內噪聲的抑制作用。所以設計積分器參數時對于各種非理想因素造成的影響要在前面模型設計中進行詳細分析,在非理想情況下,確定合適的參數值。同可變增益運放樣,積分器中也可以加入高頻調制電路,以避免低頻噪聲影響。但在調制器設計中只需要考慮第yi階積分器的噪聲即可。可以證明:假設在n階單環調制器中,第i個積分器的等效輸入噪聲為En,i,則整個調制器的等效輸入噪聲Ei可以表示為:

(6)

(6)

式(6)成立的條件是當n≥2時,調制器處于穩定狀態。其中,K1,K2,a分別為diyi及第二個積分器的增益衰減因子。從式子可以看出,除diyi階積分器之外,第i(i>1)階積分器都受到i-1階的調制作用。所以在進行調制器設計時,只需要在diyi階調制器中加入高頻調制電路。對于量化器的設計,從降低功耗角度考慮,本文采用動態鎖存比較器來實現。如圖8所示,其工作過程主要分為2個階段:預置期和再建期。在預置階段,將CLKl置為低電平,CLK2置為高電平,M11和M14導通,C、d兩點被充電到電源電壓。而開關管M2a作為復位管,電流流經M2a使得a、b兩點的電位差迅速減小,且與此時的輸入電壓差成正比。下時刻,CLKl被置為高電平,CLK2為低電平。比較器進入再建期即比較階段,將復位后a、b兩點的差值作為比較電壓的初始值,之后在正反饋作用下,a、b兩點電壓被拉到電源電壓和地,得出比較結果。

此外,在比較器設計過程中需要著重考慮復位管M2a的尺寸問題。若管子尺寸設計較小,則管子電阻變大,流過M2a的電流將減小,繼而降低了a、b兩點平衡的速度,增加了復位階段的時間;但若管子尺寸設計的較大,管子的電阻變小,使得復位后a、b兩點的電壓差較小,降低了再建速度。所以設計時應按照要求折衷考慮。比較器設計中還需要考慮到比較器的kick-back噪聲和失調的影響,其中,kickback噪聲是比較器的輸出通過管子的寄生電容耦合到輸入引起的,可以通過引入開關電容的采樣電路來降低其影響。而失調主要是由輸入管的匹配精度決定,所以在比較器的版圖設計時應注意輸入管的擺放。

由于調制器輸入擺幅設計為1V,要實現12bits的有效精度,比較器的zui小精度達到1/2個LSB即可,通過仿真,比較器能實現精度為0.1mV的比較,滿足設計要求。

3、版圖與仿真

本設計是基于SMIC0.18um混合信號CMOS工藝實現的,在3.3V電源電壓下整體電路的功耗為2.1mW,讀出電路的版圖布局,如圖9所示,面積為1.05mmX0.73mm。

圖8霍爾傳感器版圖設計

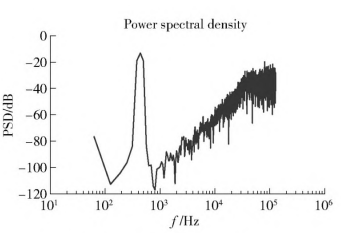

基于整體版圖設計,進行寄生參數提取,然后在輸入信號為4mV,前端放大器放大100倍,時鐘頻率為256kHz的條件下進行后仿真。仿真結果如圖10所示,信噪比為83.12dB,有效位數為13.5bits,滿足了設計的要求。

圖9讀山電路FFT分析結果

4安科瑞霍爾傳感器產品選型

4.1產品介紹

霍爾電流傳感器主要適用于交流、直流、脈沖等復雜信號的隔離轉換,通過霍爾效應原理使變換后的信號能夠直接被AD、DSP、PLC、二次儀表等各種采集裝置直接采集和接受,響應時間快,電流測量范圍寬精度高,過載能力強,線性好,抗干擾能力強。適用于電流監控及電池應用、逆變電源及太陽能電源管理系統、直流屏及直流馬達驅動、電鍍、焊接應用、變頻器,UPS伺服控制等系統電流信號采集和反饋控制。

4.2產品選型

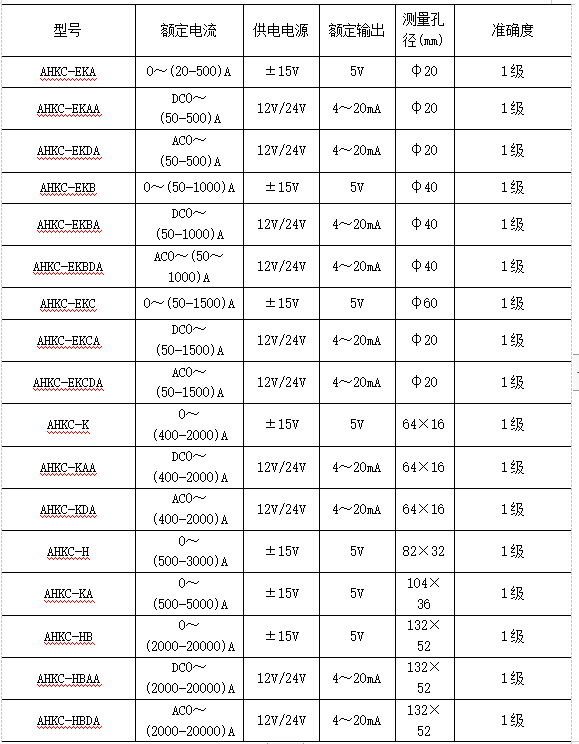

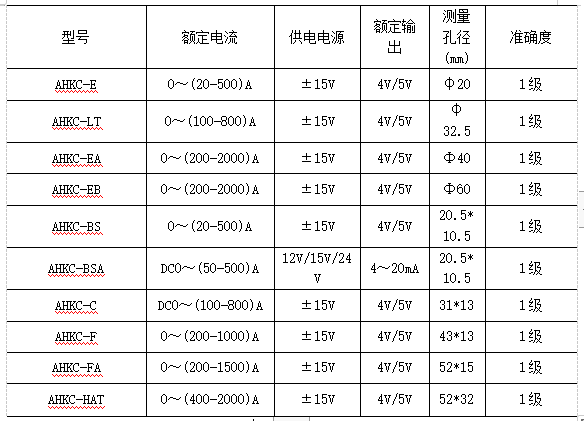

4.2.1開口式開環霍爾電流傳感器

表1

4.2.2閉口式開環霍爾電流傳感器

表2

4.2.3閉環霍爾電流傳感器

表3

4.2.4直流漏電流傳感器

表4

5實驗結論

本文基于石墨烯霍爾傳感器輸出信號的特點,完成了其讀出電路的設計。采用可變增益運算放大器對信號進行放大,再由過采樣ADC進行數據轉換與精度測量。而在整個過程中,通過高頻調制方式降低低頻噪聲以及失調的影響,以改善電路的性能。zui終在smico.18μM1P6MCOS工藝條件下,對整體電路進行測試,結果表明電路滿足12bits的設計目標。

【參考文獻】

[1] 孫海燕,趙雅靜,張曉波,戴瀾.基于高頻調制的霍爾傳感器讀出電路設計術

[2] 陳鋮穎,蔣見花,胡曉宇.種基于石墨烯霍爾器件的讀出電路設計[J].微電子學與計算機,2013,12(30):137—141.

[3] 安科瑞企業微電網設計與應用手冊2020.06版

作者簡介:劉細鳳,女,現任職于安科瑞電氣股份有限公司,主要從事隔離式柵研究發展